产品规格:

产品数量:

包装说明:

关 键 词:云存储服务器软件

行 业:电子 电子产品设计

发布时间:2021-04-12

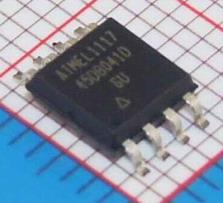

4-megabit

2.5-volt or

2.7-volt

DataFlash®

AT45DB041B

For New

Designs Use

AT45DB041D

Read Commands

By specifying the appropriate opcode, data can be read from the main memory or from either

one of the two data buffers. The DataFlash supports two categories of read modes in relation to

the SCK signal. The differences between the modes are in respect to the inactive state of the

SCK signal as well as which clock cycle data will begin to be output. The two categories, which

are comprised of four modes total, are defined as Inactive Clock Polarity Low or Inactive Clock

Polarity High and SPI Mode 0 or SPI Mode 3. A separate opcode (refer to Table 5-3 on page 10

for a complete list) is used to select which category will be used for reading. Please refer to the

“Detailed Bit-level Read Timing” diagrams in this datasheet for details on the clock cycle

sequences for each mode.

The next 11 address bits (PA10 - PA0) specify which page of the main memory array to

read, and the last nine bits (BA8 - BA0) of the 24-bit address sequence specify the starting byte

address within the page. The 32 don’t care bits that follow the 24 address bits are needed to ini�tialize the read operation. Following the 32 don’t care bits, additional clock pulses on the SCK

pin will result in serial data being output on the SO (serial output) pin.

Features

• Single 2.5V - 3.6V or 2.7V - 3.6V Supply

• Serial Peripheral Interface (SPI) Compatible

• 20 MHz Max Clock Frequency

• Page Program Operation

– Single Cycle Reprogram (Erase and Program)

– 2048 Pages (264 Bytes/Page) Main Memory

• Supports Page and Block Erase Operations

• Two 264-byte SRAM Data Buffers – Allows Receiving of Data

while Reprogramming the Flash Memory Array

• Continuous Read Capability through Entire Array

– Ideal for Code Shadowing Applications

• Low Power Dissipation

– 4 mA Active Read Current Typical

– 2 µA CMOS Standby Current Typical

• Hardware Data Protection Feature

• 5.0V-tolerant Inputs: SI, SCK, CS, RESET, and WP Pins

• Commercial and Industrial Temperature Ranges

• Green (Pb/Halide-free/RoHS Compliant) Package Options

Buffer Read

Data can be read from either one of the two buffers, using different opcodes to specify which

buffer to read from. An opcode of 54H or D4H is used to read data from buffer 1, and an opcode

of 56H or D6H is used to read data from buffer 2. To perform a Buffer Read, the eight bits of the

opcode must be followed by 15 don’t care bits, nine address bits, and eight don’t care bits. Since

the buffer size is 264 bytes, nine address bits (BFA8 - BFA0) are required to specify the first byte

of data to be read from the buffer. The CS pin must remain low during the loading of the opcode,

the address bits, the don’t care bits, and the reading of data. When the end of a buffer is

reached, the device will continue reading back at the beginning of the buffer. A low-to-high tran�sition on the CS pin will terminate the read operation and tri-state the SO pin.

Status Register Read

The status register can be used to determine the device’s Ready/Busy status, the result of a

Main Memory Page to Buffer Compare operation, or the device density. To read the status reg�ister, an opcode of 57H or D7H must be loaded into the device. After the last bit of the opcode is

shifted in, the eight bits of the status register, starting with the MSB (bit 7), will be shifted out on

the SO pin during the next eight clock cycles. The five most significant bits of the status register

will contain device information, while the remaining three least-significant bits are reserved for

future use and will have undefined values. After bit 0 of the status register has been shifted out,

the sequence will repeat itself (as long as CS remains low and SCK is being toggled) starting

again with bit 7. The data in the status register is constantly updated, so each repeating

sequence will output new data.