价格:面议

无锡珹芯电子科技有限公司

联系人:薛逸焕

电话:17521010691

地址:无锡市新吴区菱湖大道111-2号软件园飞鱼座A302室-126

在进行芯片设计时,创新和优化是永恒的主题。设计师需要不断探索新的设计理念和技术,如采用新的晶体管结构、开发新的内存技术、利用新兴的材料等。同时,他们还需要利用的电子设计自动化(EDA)工具来进行设计仿真、验证和优化。 除了技术层面的融合,芯片设计还需要跨学科的团队合作。设计师需要与工艺工程师、测试工程师、产品工程师等紧密合作,共同解决设计过程中的问题。这种跨学科的合作有助于提高设计的质量和效率。 随着技术的发展,芯片设计面临的挑战也在不断增加。设计师需要不断学习新的知识和技能,以适应快速变化的技术环境。同时,他们还需要关注市场趋势和用户需求,以设计出既创新又实用的芯片产品。 总之,芯片设计是一个多学科融合的过程,它要求设计师具备的知识基础和创新能力。通过综合运用电子工程、计算机科学、材料科学等领域的知识,设计师可以实现更高性能、更低功耗的芯片设计,推动整个行业的发展。芯片设计过程中,架构师需要合理规划资源分配,提高整体系统的效能比。江苏存储芯片IO单元库

在芯片设计的验证阶段,设计团队会进行一系列的验证测试,以确保设计满足所有规格要求和性能指标。这包括形式验证、静态时序分析和动态测试等。形式验证用于检查设计是否符合逻辑规则,而静态时序分析则用于评估信号在不同条件下的时序特性。动态测试则涉及到实际的硅片测试,这通常在芯片制造完成后进行。测试团队会使用专门的测试设备来模拟芯片在实际应用中的工作条件,以检测潜在的缺陷和性能问题。一旦设计通过所有验证测试,就会进入制造阶段。制造过程包括晶圆制造、光刻、蚀刻、离子注入、金属化和封装等步骤。每一步都需要精确控制,以确保芯片的质量和性能。制造完成后,芯片会经过测试,然后才能被送往市场。整个芯片设计过程是一个不断迭代和优化的过程,需要跨学科的知识和紧密的团队合作。设计师们不仅要具备深厚的技术专长,还要有创新思维和解决问题的能力。随着技术的不断进步,芯片设计领域也在不断发展,为人类社会带来更多的可能性和便利。江苏SARM芯片芯片运行功耗直接影响其应用场景和续航能力,是现代芯片设计的重要考量因素。

**化的芯片设计也面临着挑战。设计师需要适应不同国家和地区的商业环境、法律法规以及文化差异。此外,**供应链的管理和协调也是一项复杂任务,需要精心策划以确保设计和生产过程的顺畅。 为了克服这些挑战,设计师们需要具备强大的项目管理能力、跨文化沟通技巧和灵活的适应能力。同时,企业也需要建立有效的协作平台和流程,以支持**团队的协同工作。 随着技术的不断进步和**化程度的加深,芯片设计的国际合作将变得更加紧密。设计师们将继续携手合作,共同应对设计挑战,推动芯片技术的创新和发展,为**市场带来更高效、更智能、更环保的芯片产品。通过这种**性的合作,芯片设计领域的未来将充满无限可能。

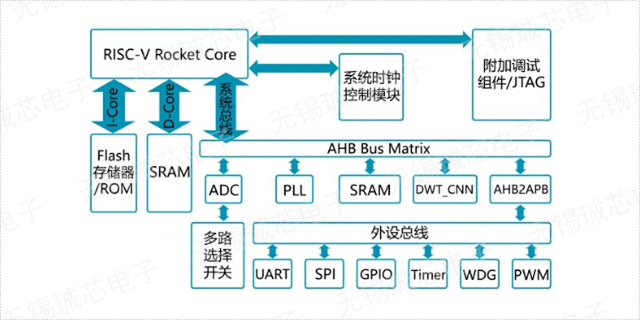

MCU的存储器MCU的存储器分为两种类型:非易失性存储器(NVM)和易失性存储器(SRAM)。NVM通常用于存储程序代码,即使在断电后也能保持数据不丢失。SRAM则用于临时存储数据,它的速度较快,但断电后数据会丢失。MCU的I/O功能输入/输出(I/O)功能是MCU与外部世界交互的关键。MCU提供多种I/O接口,如通用输入/输出(GPIO)引脚、串行通信接口(如SPI、I2C、UART)、脉冲宽度调制(PWM)输出等。这些接口使得MCU能够控制传感器、执行器和其他外部设备。MCU芯片和AI芯片的深度融合,正在推动新一代智能硬件产品的创新与升级。

除了晶体管尺寸的优化,设计师们还在探索新的材料和架构。例如,采用高介电常数材料和金属栅较技术可以进一步提高晶体管的性能,而多核处理器和异构计算架构的设计则可以更有效地利用芯片的计算资源,实现更高的并行处理能力。 此外,随着人工智能和机器学习技术的发展,芯片设计也开始融入这些新兴技术。专门的AI芯片和神经网络处理器被设计出来,它们针对深度学习算法进行了优化,可以更高效地处理复杂的数据和执行机器学习任务。 在设计过程中,设计师们还需要考虑芯片的可靠性和安全性。通过采用冗余设计、错误校正码(ECC)等技术,可以提高芯片的容错能力,确保其在各种环境下的稳定运行。同时,随着网络安全形势的日益严峻,芯片设计中也越来越多地考虑了安全防护措施,如硬件加密模块和安全启动机制等。高质量的芯片IO单元库能够适应高速信号传输的需求,有效防止信号衰减和噪声干扰。江苏MCU芯片运行功耗

深度了解并遵循芯片设计流程,有助于企业控制成本、提高良品率和项目成功率。江苏存储芯片IO单元库

随着半导体技术的不断进步,芯片设计领域的创新已成为推动整个行业发展的关键因素。设计师们通过采用的算法和设计工具,不断优化芯片的性能和能效比,以满足市场对于更高性能和更低能耗的需求。 晶体管尺寸的缩小是提升芯片性能的重要手段之一。随着制程技术的发展,晶体管已经从微米级进入到纳米级别,这使得在相同大小的芯片上可以集成更多的晶体管,从而大幅提升了芯片的计算能力和处理速度。同时,更小的晶体管尺寸也意味着更低的功耗和更高的能效比,这对于移动设备和数据中心等对能耗有严格要求的应用场景尤为重要。江苏存储芯片IO单元库